[비즈니스포스트] “차량용 반도체 시장에 최적화된 공정을 적기에 개발해 자율주행 단계별 인공지능 반도체부터 전력반도체, MCU(마이크로 컨틀롤러 유닛) 등을 고객의 요구에 맞춰 양산할 것이다.”

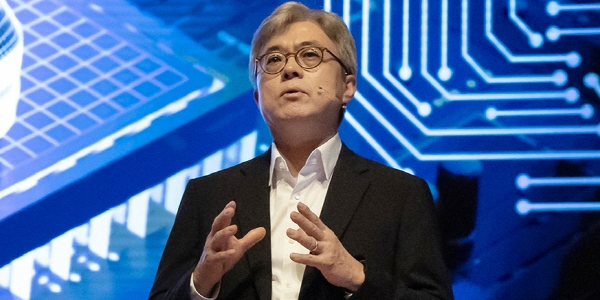

최시영 삼성전자 파운드리사업부장 사장은 19일 독일 뮌헨에서 열린 ‘삼성전자 파운드리 포럼 2023’에서 이 같은 내용을 포함해 최첨단 공정 로드맵과 전장을 비롯한 수요처별 파운드리 전략을 공개했다고 삼성전자가 전했다.

![삼성전자 2나노 전장용 반도체 2026년 양산 준비, 최시영 "자율주행 선도"]()

최 사장은 “삼성전자만의 차별화된 파운드리 솔루션으로 전기차와 자율주행차 시대를 선도하겠다”고 말했다.

우선 최첨단 2나노 전장솔루션 양산 준비를 2026년 마무리 짓고 차세대 내장형 M램(eMRAM) 포트폴리오를 확대한다는 계획을 내놨다.

eMRAM은 빠른 읽기와 쓰기속도를 기반으로 높은 온도에서도 안정적으로 구동이 가능한 메모리반도체로 자동차 전장분야 시스템반도체에서 쓰임새가 확대될 것으로 예상된다.

삼성전자는 2019년 반도체업계 최초로 28나노 eMRAM을 양산한 바 있다.

2023년 현재기준으로는 자동차부품협회의 신뢰성 평가 기준을 바탕으로 핀펫(FinFET)공정에 기반한 14나노 eMRAM을 개발하고 있다.

또한 2026년 8나노, 2027년에는 5나노까지 eMRAM 포트폴로오를 확대한다는 계획도 알렸다. 8나노 eMRAM의 경우 이전 14나노와 비교해 집적도는 30%, 속도는 33%가 증가할 것으로 예상된다.

최 사장은 삼성전자의 8인치 BCD공정 포트폴리오도 강화한다는 계획도 알렸다.

BCD공정은 아날로그 신호제어(Bipolar), 디지털 신호제어(CMOS), 고전압관리(DMOS) 트랜지스터를 하나의 칩에 구현한 것으로 주로 전력반도체 생산에 활용된다.

삼성전자는 현재 양산중인 130나노 전장 BCD 공정을 2025년 90나노까지 확대하기로 했다. 90나노 전장 BCD 공정은 130나노와 비교해 약 20% 칩 면적 감소가 기대된다.

최 사장은 트랜지스터 사이 간격을 줄이고 전력누출과 과전류에 따라 소자 특성이 저하되는 현상을 개선시키는 DTI 기술을 활용하는 계획도 설명했다.

삼성전자는 DTI기술을 활용해 전장에 들어가는 반도체 솔루션에 적용되는 고전압을 기존 70볼트에서 120볼트로 높인다는 목표를 세웠다. 이를 통해 130나노 BCD 공정에 120볼트를 적용한 공정설계키트(PDK)를 2025년 제공한다.

또한 최 사장은 20개 파트너와 함께 최첨단 패키지 협의체를 구축한 것을 바탕으로 2.5D, 3D 패키지 솔루션을 개발해 나가겠다고 밝혔다. 이를 통해 전장과 고성능 컴퓨팅(HPC) 분야에서 선도적 위치를 다져간다는 목표를 세웠다.

삼성전자는 이번 독일 행사외에도 미국, 한국, 일본에서도 '삼성 파운드리 포럼 2023'을 개최한 바 있다. 삼성전자는 오프라인 행사에 참석하지 못한 글로벌 고객을 위해서 11월2일부터 올해 말까지 삼성전자 반도체 공식 홈페이지에 행사 내용을 공개한다. 조장우 기자

최시영 삼성전자 파운드리사업부장 사장은 19일 독일 뮌헨에서 열린 ‘삼성전자 파운드리 포럼 2023’에서 이 같은 내용을 포함해 최첨단 공정 로드맵과 전장을 비롯한 수요처별 파운드리 전략을 공개했다고 삼성전자가 전했다.

▲ 최시영 삼성전자 파운드리사업부장 사장이 자율주 시대를 선도하겠다고 자신감을 보였다. <삼성전자>

최 사장은 “삼성전자만의 차별화된 파운드리 솔루션으로 전기차와 자율주행차 시대를 선도하겠다”고 말했다.

우선 최첨단 2나노 전장솔루션 양산 준비를 2026년 마무리 짓고 차세대 내장형 M램(eMRAM) 포트폴리오를 확대한다는 계획을 내놨다.

eMRAM은 빠른 읽기와 쓰기속도를 기반으로 높은 온도에서도 안정적으로 구동이 가능한 메모리반도체로 자동차 전장분야 시스템반도체에서 쓰임새가 확대될 것으로 예상된다.

삼성전자는 2019년 반도체업계 최초로 28나노 eMRAM을 양산한 바 있다.

2023년 현재기준으로는 자동차부품협회의 신뢰성 평가 기준을 바탕으로 핀펫(FinFET)공정에 기반한 14나노 eMRAM을 개발하고 있다.

또한 2026년 8나노, 2027년에는 5나노까지 eMRAM 포트폴로오를 확대한다는 계획도 알렸다. 8나노 eMRAM의 경우 이전 14나노와 비교해 집적도는 30%, 속도는 33%가 증가할 것으로 예상된다.

최 사장은 삼성전자의 8인치 BCD공정 포트폴리오도 강화한다는 계획도 알렸다.

BCD공정은 아날로그 신호제어(Bipolar), 디지털 신호제어(CMOS), 고전압관리(DMOS) 트랜지스터를 하나의 칩에 구현한 것으로 주로 전력반도체 생산에 활용된다.

삼성전자는 현재 양산중인 130나노 전장 BCD 공정을 2025년 90나노까지 확대하기로 했다. 90나노 전장 BCD 공정은 130나노와 비교해 약 20% 칩 면적 감소가 기대된다.

최 사장은 트랜지스터 사이 간격을 줄이고 전력누출과 과전류에 따라 소자 특성이 저하되는 현상을 개선시키는 DTI 기술을 활용하는 계획도 설명했다.

삼성전자는 DTI기술을 활용해 전장에 들어가는 반도체 솔루션에 적용되는 고전압을 기존 70볼트에서 120볼트로 높인다는 목표를 세웠다. 이를 통해 130나노 BCD 공정에 120볼트를 적용한 공정설계키트(PDK)를 2025년 제공한다.

또한 최 사장은 20개 파트너와 함께 최첨단 패키지 협의체를 구축한 것을 바탕으로 2.5D, 3D 패키지 솔루션을 개발해 나가겠다고 밝혔다. 이를 통해 전장과 고성능 컴퓨팅(HPC) 분야에서 선도적 위치를 다져간다는 목표를 세웠다.

삼성전자는 이번 독일 행사외에도 미국, 한국, 일본에서도 '삼성 파운드리 포럼 2023'을 개최한 바 있다. 삼성전자는 오프라인 행사에 참석하지 못한 글로벌 고객을 위해서 11월2일부터 올해 말까지 삼성전자 반도체 공식 홈페이지에 행사 내용을 공개한다. 조장우 기자

![[여론조사꽃] 이재명 지지율 73.6%로 2.9%p 내려, 민주당 55.9% vs 국힘 24.5%](https://businesspost.co.kr/news/photo/202605/20260511111534_53025.jpg)