▲ 대만 TSMC 본사 및 반도체 웨이퍼 이미지.

TSMC가 기술적 한계에 직면해 고객사들의 반도체 위탁생산 주문을 확보하는 데 어려움을 겪는 사이 삼성전자가 자체 3나노 공정을 통해 장기간 기술 우위를 차지할 가능성이 커졌다.

증권전문지 시킹알파는 28일 “TSMC가 5나노 반도체 미세공정 도입 이후에 과거 인텔이 10나노 공정에서 마주한 것과 비슷한 기술 장벽에 부딪히고 있는 것으로 보인다”고 보도했다.

시킹알파는 반도체 공정기술 전문 조사기관 앙스트로노믹스 분석을 인용해 TSMC가 현재 파운드리사업에 주력으로 활용하는 5나노 미세공정이 기대 이하의 성능을 나타내고 있다고 전했다.

TSMC가 2018년에 5나노 미세공정을 도입하며 발표한 내용과 달리 반도체 회로폭이 기존 7나노 공정과 비교해 크게 좁아지지 않았고 따라서 성능 개선폭도 기대치를 밑돌았다는 것이다.

앙스트로노믹스는 TSMC 5나노 공정에서 생산된 애플 ‘M1맥스’와 화웨이 ‘기린9000’ 등 프로세서의 반도체 미세공정 수준이 모두 발표된 내용과 비교해 뒤떨어진다는 조사결과를 내놓았다.

TSMC가 5나노 미세공정과 관련해 잘못된 측정 기준을 사용했거나 의도적으로 이런 내용을 허위로 발표했을 가능성을 제시한 셈이다.

앙스트로노믹스는 이를 근거로 볼 때 TSMC가 최근 하반기 도입을 앞둔 3나노 미세공정과 관련해 내놓은 발표도 신뢰성을 검증해야 할 필요가 있다고 바라봤다.

TSMC는 최근 반도체 기술포럼을 열고 올해 처음으로 도입하는 3나노 파운드리 공정을 N3E와 N3S 등 모두 다섯 가지의 파생 공정으로 나눠 순차적으로 선보인다는 계획을 내놓았다.

다만 앙스트로노믹스는 TSMC 3나노 파생 공정이 초기 3나노 미세공정과 비교해 뚜렷한 성능 발전을 나타내지 않을 수 있다며 차세대 2나노 공정 성능 개선폭도 크지 않을 가능성을 제시했다.

TSMC가 이미 5나노 공정 기술에서 신뢰를 잃은 만큼 앞으로 선보일 차기 공정에서 약속한 수준의 성능 발전을 선보일 수 있을지도 불투명하다는 것이다.

시킹알파는 “반도체업계에서 TSMC의 3나노 미세공정에 기대하던 수준의 성능 발전폭은 2026년 2나노 공정에서야 현실화될 수 있을 것”이라며 “TSMC가 파운드리시장에서 기술 선두 지위와 경쟁력을 잃을 수 있다”고 보도했다.

앙스트로노믹스가 진행한 조사는 반도체 회로폭을 직접 이미지화해 측정할 수 있는 신기술을 활용해 진행됐다. 사실상 처음으로 TSMC의 미세공정 기술에 확실한 검증이 이뤄진 셈이다.

TSMC가 해당 조사결과를 계기로 파운드리 주요 고객사들에 신뢰를 잃고 기술 리더십을 유지하기도 어려워진다면 자연히 파운드리 최대 경쟁사인 삼성전자에 반사이익이 돌아올 수 있다.

앙스트로노믹스는 삼성전자의 4나노 반도체 미세공정도 기존 5나노 공정과 비교해 회로 개선폭이 매우 미미한 수준이었다며 생산 능력과 수율 등에서도 약점을 안고 있다고 바라봤다.

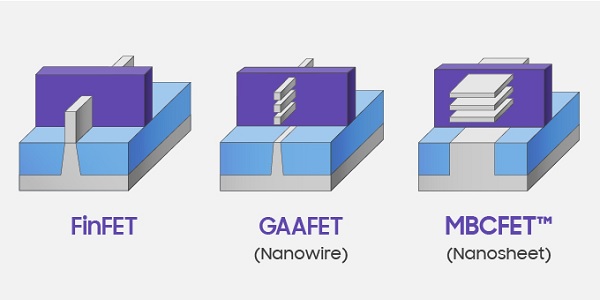

▲ 삼성전자 반도체 파운드리 미세공정에 활용되는 기술 안내.

삼성전자가 3나노 공정에 파운드리업계 최초로 반도체 미세공정 한계를 뛰어넘을 수 있는 GAA(게이트올어라운드) 및 MBCFET(멀티브릿지FET) 신기술을 도입하기로 했기 때문이다.

GAA 및 MBCFET 공정은 반도체 회로폭이 좁아져도 높은 성능을 낼 수 있고 공간을 효율적으로 활용할 수 있도록 해 미세공정 반도체 설계에 유연성을 높일 수 있는 기술이다.

삼성전자가 신기술을 통해 반도체 미세공정 회로폭을 더욱 좁히는 데 성과를 내거나 회로폭이 크게 좁아지지 않아도 충분히 높은 성능을 구현할 수 있다는 점을 증명할 수 있다.

TSMC는 2나노 공정부터 GAA 기술 도입을 계획하고 있는 만큼 삼성전자가 3나노 공정 도입을 계기로 최소한 수 년 동안 절대적 기술 우위를 지켜낼 수 있는 발판을 마련한 셈이다.

다만 인텔이 최근 미세공정 기술 발전에 업계의 예상을 뛰어넘는 성과를 내면서 파운드리업계 ‘다크호스’로 떠오르고 있다는 점이 삼성전자에 위협을 키우고 있다.

시킹알파에 따르면 인텔은 앞으로 도입하는 인텔4 및 인텔3 공정 반도체의 회로폭을 크게 줄여 나가면서 기술 선두 지위를 확보하겠다는 목표를 세우고 있다.

인텔이 현재 제시하고 있는 기술 발전 목표를 달성한다면 내년 2분기부터 TSMC와 삼성전자를 모두 제치고 최소한 2026년까지 공정 기술력에서 최고 기업으로 거듭날 수 있다.

그러나 인텔이 제시한 목표가 다소 비현실적이라는 평가도 일각에서 나오고 실제로 반도체 양산을 통해 검증을 받지 않은 만큼 실제로 기술 발전을 순조롭게 이뤄낼 수 있을지는 불투명하다.

앙스트로노믹스는 앞으로 삼성전자 및 인텔의 미세공정 반도체를 대상으로도 정밀 측정과 조사를 통해 그동안 기술 발전에 얼마나 성과를 냈는지 검증하겠다는 계획을 제시했다. 김용원 기자

![[여론조사꽃] 이재명 지지율 73.6%로 2.9%p 내려, 민주당 55.9% vs 국힘 24.5%](https://businesspost.co.kr/news/photo/202605/20260511111534_53025.jpg)