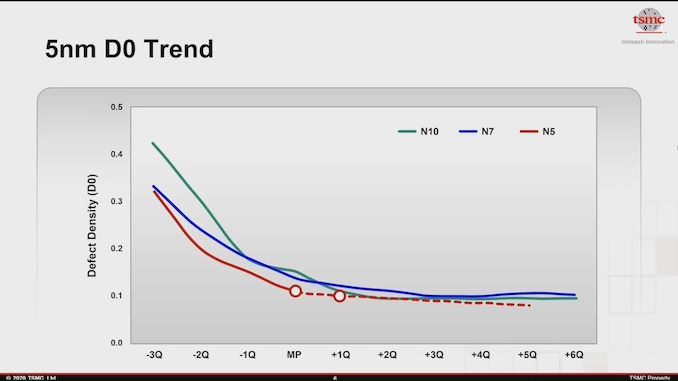

▲ TSMC 반도체 공정별 단위면적당 결함 밀도. 개발 기간이 같을 때 5나노급 공정(빨간색)이 7나노급(파란색), 10나노급(초록색)보다 낮은 결함을 보인다. < TSMC >

26일 IT매체 아난드테크에 다르면 TSMC는 최근 열린 기술심포지엄을 통해 5나노급 공정에서 웨이퍼 1㎠당 0.10~0.11개의 결함을 보이고 있다고 밝혔다.

아난드테크는 “현재 TSMC의 5나노급 공정은 개발기간을 놓고 보면 7나노급 공정보다 결함이 적다”고 말했다.

앞서 TSMC 7나노급 공정은 양산체계를 갖춘 뒤 3분기가 지나서야 1㎠당 0.09개 결함을 보였다.

5나노급 공정은 현재 양산에 들어갔는데 앞으로 1분기가 지나면 1㎠당 결함이 0.10개 미만으로 줄어들 것으로 예상됐다.

아난드테크는 TSMC가 극자외선(EUV) 기술을 더 많이 사용해 수율을 개선했다고 봤다.

TSMC는 5나노급 반도체를 본격적으로 양산하는 한편 3나노급, 2나노급 공정도 준비하고 있다.

대만 디지타임스에 따르면 TSMC는 2022년 하반기 3나노급 반도체 양산을 시작한다. 또 2나노급 파운드리공장 건설을 위한 부지를 이미 확보했다. [비즈니스포스트 임한솔 기자]

![[현장] 일본판 쥬라기공원 '정글리아' 가보니, 어른도 혹할 '공룡 세계'는 진행형](https://businesspost.co.kr/news/photo/202605/20260511154758_246164.png)