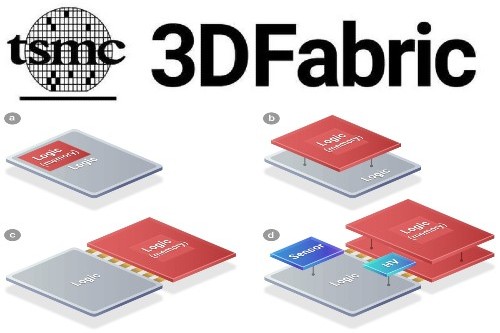

▲ TSMC가 출원한 상표 '3D패브릭(위쪽)'과 TSMC 3D 패키징 기술 'SoIC' 사용 예시. < TSMC >

패키징은 반도체를 최종적으로 탑재되는 제품에 알맞게 형태를 만드는 공정을 말한다. 패키징 과정에서 반도체를 얼마나 효율적으로 배치하고 연결하느냐에 따라 반도체를 탑재하는 기기의 성능이 달라질 수 있다.

삼성전자와 TSMC 가운데 어느 쪽이 더 우수한 패키징 기술을 선보일지가 파운드리 고객사를 끌어오는 데 중요한 요인이 될 것으로 전망된다.

25일 반도체업계에 따르면 TSMC는 최근 미국특허청(USPTO)에서 반도체사업에 관해 ‘3D패브릭(3D FABRIC)’이라는 상표를 출원했다.

3D패브릭은 TSMC가 개발하는 ‘SoIC(시스템온IC)’ 등 3D패키징 기술을 나타내는 것으로 파악된다.

IT매체 톰스하드웨어는 “TSMC는 이미 3D패키징 기술 포트폴리오를 보유하고 있다”며 “3D패브릭은 고대역폭 메모리반도체(HBM) 등 특수한 설계자산을 패키지로 묶는 기술에 관한 새로운 브랜드체계로 보인다”고 말했다.

시스템반도체와 메모리반도체 등 반도체는 서로 거리가 멀면 데이터 전송속도 등이 떨어져 제품 성능이 감소한다. 이를 개선하기 위해 ‘시스템인패키지(SIP)’ 방식이 사용된다. 한 기판 위에서 서로 다른 여러 반도체를 연결해 패키징하는 기술이다.

기존 시스템인패키지에서는 중앙처리장치(CPU)·그래픽처리장치(GPU), 센서를 비롯한 시스템반도체와 메모리반도체 등을 2D 평면에 나란히 놓는 구조가 주로 사용돼 왔다.

최근에는 D램을 수직으로 쌓은 고대역폭 메모리반도체가 시스템인패키지에 적용되면서 2D구조가 2.5D로 개선됐다. 적층한 메모리반도체와 평면에 놓인 시스템반도체를 연결해 성능을 개선할 수 있게 됐다는 의미다.

SoIC와 같은 3D패키징 기술은 여기에서 한 걸음 더 나아가 시스템반도체도 쌓는 것을 목표로 한다. 메모리반도체와 시스템반도체를 함께 쌓아 제품 부피를 더욱 줄이면서 성능을 높이기 위한 것이다.

3D패키징 기술을 적용하면 한 패키지 안에서 더 많은 시스템반도체를 통합할 수 있어 유연한 반도체 설계가 가능하다는 장점도 있다.

TSMC는 “SoIC 플랫폼은 현재 첨단 패키징 솔루션과 비교해 더 작은 제품 형태, 더 높은 대역폭, 더 낮은 전력 소비 등의 장점을 지니고 있다”고 설명했다.

▲ 삼성전자가 개발한 3D 패키징 기술 '엑스큐브' 이미지. <삼성전자 유튜브 채널>

삼성전자는 13일 3D패키징 기술 ‘엑스큐브’를 적용한 시험 제품을 생산하는 데 성공했다고 발표했다. 수직으로 쌓은 시스템반도체와 메모리반도체에 미세한 구멍을 뚫어 서로 연결하는 방식을 채택했다.

삼성전자는 “고객사는 삼성전자가 제공하는 설계도구를 활용해 엑스큐브 기반 반도체 개발을 바로 시작할 수 있다”며 “엑스큐브 기술은 고성능 반도체를 요구하는 분야는 물론 스마트폰과 입는(웨어러블)기기의 경쟁력을 높이는 핵심기술로 활용될 것”이라고 말했다.

현재 삼성전자와 TSMC의 반도체 미세공정 개발은 거의 평행선을 그리고 있다. 두 기업은 최근 5나노급 반도체 양산을 시작했다.

여기에 더해 TSMC는 최근 열린 기술심포지엄에서 3나노급 반도체를 2021년 위험생산(파운드리가 생산비용을 부담하는 과정)하고 2022년 하반기 양산한다는 일정을 발표했다. 삼성전자도 비슷한 과정을 거쳐 3나노급 반도체 양산에 들어가는 것으로 파악된다.

하지만 모든 파운드리 고객사가 무조건 더 미세한 공정을 채택하기는 어렵다. 새로운 공정을 기반으로 반도체를 설계할 때마다 짧지 않은 연구기간과 막대한 비용이 필요하기 때문이다.

시장 조사기관 IBS에 따르면 반도체기업들이 10나노급 반도체를 설계하는 데 평균적으로 1억7400만 달러가 들었다. 7나노급은 3억 달러, 5나노급은 5억3천만 달러가 필요했다. 3나노급 공정에서는 반도체 설계에만 5억~15억 달러가 투입될 것으로 전망된다.

반도체전문 매체 세미콘덕터엔지니어링은 “전통적 반도체 설계는 점점 더 복잡해지고 비싸진다”며 “많은 반도체 공급사들이 이를 대체하기 위해 고급 패키징 기술을 모색하고 있다”고 말했다.

반도체기업들이 위탁생산을 맡기는 과정에서 미세공정뿐 아니라 우수한 패키징 기술을 염두에 둘 수 있다는 뜻이다.

삼성전자가 TSMC를 따라잡을 만큼 고객사를 확보할 수 있을지가 패키징 분야에서 결정될 여지가 있는 셈이다.

시장 조사기관 트렌드포스는 TSMC가 3분기 매출 113억5천만 달러를 거둬 파운드리시장 점유율 53.9%를 차지할 것으로 내다봤다. 삼성전자는 매출 36억6500만 달러, 점유율 17.4%에 그쳐 2위에 머무를 것으로 전망됐다. [비즈니스포스트 임한솔 기자]

![[코스피 5천 그늘①] 증시 활황에도 못 웃는 LG그룹, 구광모 '체질 개선'과 '밸류업'으로 저평가 끊나](https://businesspost.co.kr/news/photo/202602/20260209151542_142553.jpg)

![[코스피 5천 그늘②] 롯데그룹 주주 흥 돋는 카드 안 보인다, 신동빈 유통·화학 계열사 '시장 소외'에 속앓이](https://businesspost.co.kr/news/photo/202601/P_20260127151310_76677.jpg)